1자리의 이진수를 연산하는 Half Adder 를 살펴보겠습니다.

아래의 진리표를 봐주세요

| INPUT | OUTPUT | ||

| A | B | Carry | Sum |

| 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Half Adder 의 경우

Carry는 INPUT 모두 1인경우 1을 출력하는 AND Gate 로 표현 할 수 있습니다.

Carry = AB

Sum은 INPUT 중 1의 개수가 홀수일 때 출력하는 OR Gate 로 표현 할 수 있습니다.

Sum = A ⊕ B = A'B + AB'

Gate level

Verilog

TESTBENCH

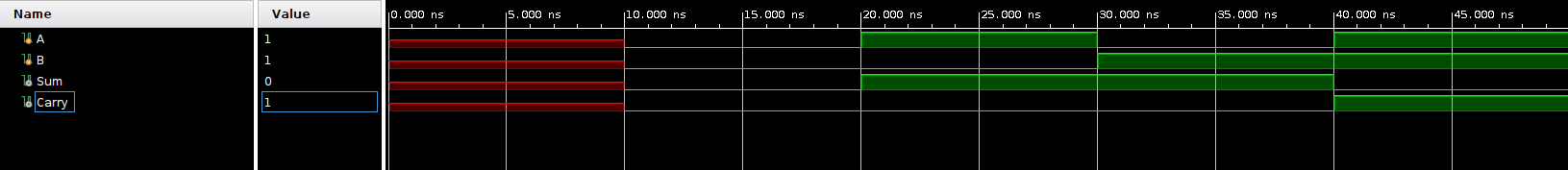

SIM

'디지털논리회로' 카테고리의 다른 글

| Full Subtractor ( # Verilog ) (0) | 2024.06.19 |

|---|---|

| Half Subtractor ( # Verilog ) (0) | 2024.06.19 |

| Full Adder ( # Verilog ) (0) | 2024.06.19 |

| 기초 게이트 (2) (0) | 2024.06.15 |

| 기초 게이트 ( 1 ) (0) | 2024.06.15 |