Datapath를 살펴보도록 하겠습니다.

Readme

Synthesis된 하드웨어의 모습을 보기 위해 Quartus로 설계하였습니다. RISC 문서를 통해 자세히 설계해야하지만, 인터페이스만을 통해 설계하기에 Imm Gen, Control unit, Mux 1개를 제외하고 설계하였습니다. R type 동작 및 테스트를 목표로 두었으며 나중에 제외한 모듈을 추가할 수 있도록 설계했습니다. RISC-V 에서는 Pipeline을 사용합니다. Fetch, Decode, Execute,Writeback 등으로 단계를 나누므로 General한 디자인을 위해 Instruction Fetch 와 Datapath로 나누어 instance를 생성했습니다.

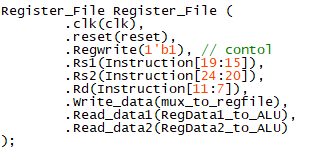

Datapath는 Register file, ALU, ALU_Control, Datamem, Mux등으로 구성하였습니다.

RISC - R type

| func7 [31 :25] | rs1 [24 : 20] | rs2 [19 : 15] | func3 [14 : 12] | rd [11 : 7] | OPcode [6 : 0] |

Instruction Memory 에서 출력되는 데이터를 R format에 맞게 나누어줍니다.

원래라면 OPcode를 Control Unit에서 Decode하게 되지만 제외하고 설계하였기에 OPcode를 ALU_control_unit에서 이용합니다. case문을 통하여 구현하였습니다.

ALU control의 출은 ALU의 OPcode로 들어가며 논리 혹은 산술연산을 선택합니다.

ALU의 결과값은 Data Memory의 주소로 들어가며 Read 혹은 Write를 할 수 있습니다.

원래라면 Control Unit에서 제어해야 했을 신호들을 1혹은 0으로 고정시켜주었습니다.

reset을 통해 메모리를 초기화시켜주고 Instruction memoy값을 넣어주었습니다.

데이터 흐름을 통해 시그널들을 나열해서 봤을 때 정상작동하는것을 알 수 있습니다.

ALU_control 과 ALU는 Combinational logic, Datamem과 Register file은 register, mux 등으로 이루어진 것을 확인 할 수 있습니다.

'Verilog' 카테고리의 다른 글

| RISC ( # R- Type #Timing # Power # Verilog ) (0) | 2024.08.20 |

|---|---|

| RISC ( # R- Type # Fetch # Verilog ) (0) | 2024.07.31 |

| ECC ( Error colection code ) (2) (0) | 2024.07.04 |

| ECC ( Error colection code ) (0) | 2024.07.04 |

| Parity bit (0) | 2024.07.04 |